library ieee;

use ieee.std_logic_1164.all;

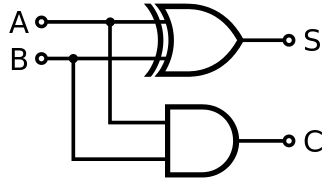

entity ha is

port(a,b:in bit;

sum,carry:out bit);

end ha;

architecture desc of ha is

begin

sum<= a xor b;

carry <= a and b;

end desc;

library ieee;

use ieee.std_logic_1164.all;

entity fa is

port(a,b,c:in bit;

sum,carry:out bit);

end fa;

architecture desc of fa is

begin

sum <= a xor b xor c;

carry<= ( a and b) or ( a and c) or (b and c);

end desc